Product Summary

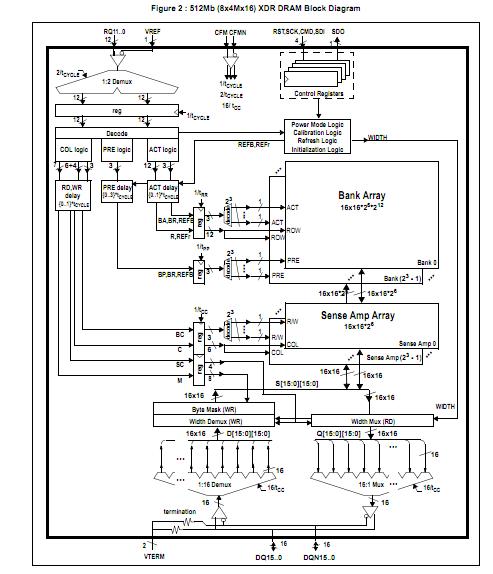

The K4Y50084UE-JCB3 is a general-purpose high-performance memory device suitable for use in a broad range of applications, including computer memory, graphics, video, and any other application where high bandwidth and low latency are required. The 512Mb XDR DRAM device is a CMOS DRAM organized as 32M words by 16bits. The use of Differential Rambus Signaling Level(DRSL) technology permits 4000/3200/2400 Mb/s transfer rates while using conventional system and board design technologies.

Features

K4Y50084UE-JCB3 features: (1)Highest pin bandwidth available; (2)Bi-directional differential RSL(DRSL); (3)On-chip termination; (4)Highest sustained bandwidth per DRAM device; (5)Low Latency ; (6)Low Power; (7)0.49us refresh intervals(32K/16ms refresh); (8)RoHS compliant.

Diagrams

(China (Mainland))

(China (Mainland))