Product Summary

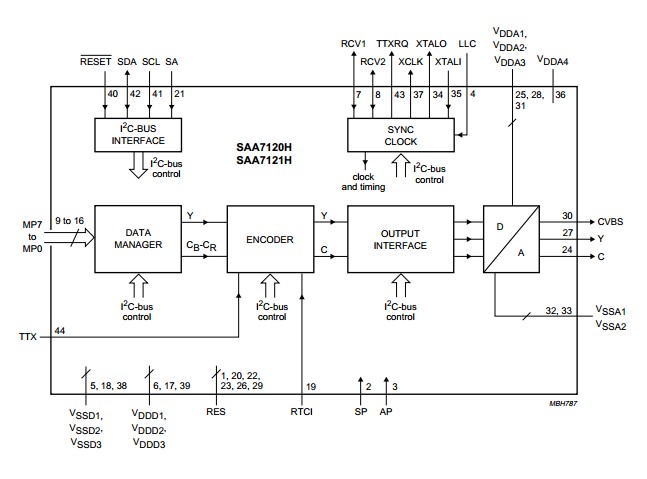

The SAA7121HV2557 is a Digital video encoder. The SAA7121HV2557 accepts CCIR compatible YUV data with 720 active pixels per line in 4 : 2 : 2 multiplexed formats, for example MPEG decoded data. It includes a sync/clock generator and on-chip DACs.

Parametrics

SAA7121HV2557 absolute maximum ratings: (1)VDDA analog supply voltage: 3.1 to 3.5 V; (2)VDDD digital supply voltage: 3.0 to 3.6 V; (3)IDDA analog supply current: 55mA; (4)IDDD digital supply current: 32mA; (5)Vi input signal voltage levels: TTL compatible; (6)Vo(p-p) analog output signal voltages Y, C and CVBS without load; (7)(peak-to-peak value): 1.35V; (8)RL load resistance: 75 to 300Ω; (9)LElf(i) low frequency integral linearity error: ±3 LSB; (10)LElf(d) low frequency differential linearity error: ±1 LSB; (11)Tamb ambient temperature: 0 to 70℃.

Features

SAA7121HV2557 features: (1)Monolithic CMOS 3.3 V device; (2)Digital PAL/NTSC encoder; (3)System pixel frequency 13.5 MHz; (4)Accepts MPEG decoded data on 8-bit wide input port; input data format CB-Y-CR (CCIR 656); (5)Three Digital-to-Analog Converters (DACs) for Y, C and CVBS two times oversampled with 10-bit resolution; (6)Real-time control of subcarrier; (7)Cross-colour reduction filter; (8)Closed captioning encoding and World Standard Teletext (WST) and North-American Broadcast Text System (NABTS) teletext encoding including sequencer and filter; (9)Line 23 Wide Screen Signalling (WSS) encoding; (10)Fast I2C-bus control port (400 kHz); (11)Encoder can be master or slave; (12)Programmable horizontal and vertical input synchronization phase; (13)Programmable horizontal sync output phase; (14)Internal Colour Bar Generator (CBG); (15)2 × 2 bytes in lines 20 (NTSC) for copy guard management system can be loaded via I2C-bus; (16)Down mode of DACs.

Diagrams

(China (Mainland))

(China (Mainland))